# KA48 System Board Specification

Order Number KA48-0-DBF

Revision/Update Information: X.01

John Kirk MLO5-2/B6 223-4690 MAST::KIRK

5-SEP-1991 08:52:02.34

© 1991 by Digital Equipment Corporation

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may occur in this document.

This specification does not describe any program or product which is currently available from Digital Equipment Corporation, nor does Digital Equipment Corporation commit to implement this specification in any program or product. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

This document was prepared using VAX DOCUMENT, Version 1.2

# Chapter 1 INTRODUCTION

# **1.1 Scope of Document**

This document specifies the functional characteristics of the KA48-AA System Module.

# **1.2 General Description**

The KA48-AA System Module forms the basis for one system:

- The VS4000 VLC single-user engineering workstation, which includes an LK401 keyboard, a VSXXX-AA mouse or VSXXX-AB tablet, SCSI and Ethernet controllers and four serial line controller. A daughter module plugs into the system module to provide an 8-plane video frame buffer and DAC that can support monochrome (single plane or gray scale) or color monitors.

- A variety of monitors support monochrome and color displays, see Chapter 13, Section 13.6.

Each VS4000 VLC is housed in a desktop enclosure which contains a KA48-AA system board, a ???? video/sound module and an H7109 power supply. The KA48-AA system board contains the following standard components:

- DC 222 (SOC) processor with integral FPA and cache

- Sockets for 8, 16 or 24 MBytes of RAM memory (2, 4 or 6 in alternative configuration)

- 256 Kbyte ROM memory (socketed)

- 32-byte network address ROM (socketed)

- time-of-year clock including 50 bytes of non-volatile RAM

- four asynchronous serial ports for keyboard mouse or tablet printer

INTRODUCTION 1-1

communications (includes full modem control)

- controller for Transceiver cable connect Ethernet network

- SCSI controller

- graphics hardware assist integrated within the RAM controller

- 8-plane frame buffer, 1024 x 1024 capability (daughter module)

The ???? contains the following components:

- Video RAMs for 8-plane 1K x 1K display

- RAMDAC

- Sound I/O chip

- Keyboard, Mouse/Tablet/Sound I-O connectors

- HALT push-button

- Alternate Console Select Switch

1-2 INTRODUCTION

# **1.3 Applicable Documents**

The following documents describe the principal LSI chips which are used in the VS4000 VLC:

| A-PS-2132064-0-0  | DC 222 (SOC) processor chip               |

|-------------------|-------------------------------------------|

| A-PS-21-34159-0-0 | DC7201, memory/graphics/IO controller.    |

| A-PS-21-35025-0-0 | , logic compaction array #1.              |

| A-PS-21-35024-0-0 | DC7238, logic compaction array #2.        |

| A-PS-2121672-0-0  | LANCE Ethernet Controller chip            |

| A-PS-2118795-0-0  | MC146818 Watch chip                       |

| A-PS-2131889-0-0  | 53C94 SCSI Interface chip                 |

| A-PS-23365A1-0-0  | Ethernet Network Address ROM              |

| A-PS-2132756-0-0  | 79C30 (Sound Chip)                        |

| A-PS-21-????-0-0  | BT458, Video Digital to Analog Convertor. |

The following documents specify the cables to external equipment to be used with the system:

| A-PS-1700300-0-0 | BCC16E cable for printer         |

|------------------|----------------------------------|

| A-PS-1700568-0-0 | BC18P cable for monochrome video |

| A-PS-1701480-0-0 | BC19S cable for color video      |

The following documents describe other components to be used with the system:

| A-SP-H7109     | Power supply and fan unit           |

|----------------|-------------------------------------|

| A-SP-LK401-0-0 | LK401 keyboard                      |

| A-SP-VRXXX-A-0 | MONO 14" 14-inch monochrome monitor |

| A-SP-VRXXX-A-0 | VR319 19-inch monochrome monitor    |

| A-SP-VRXXX-A-0 | VRC16 16-inch color monitor         |

| A-PS0-0        | VRT19 19-inch color monitor         |

| A-PS0-0        | VSXXX-AA mouse                      |

| A-PS0-0        | VSXXX-AB tablet                     |

|                |                                     |

The following documents describe the firmware in the system ROM:

VS4000 VLC System Firmware Specification VS4000 VLC Power On Initialization VS4000 VLC System Exerciser specification VMB Specification for VS4000 VLC

The following Digital Standards documents contain material applicable to this system:

| DEC STD 002 | AC Power Wiring                               |

|-------------|-----------------------------------------------|

| DEC STD 032 | VAX Architecture Standard                     |

| DEC STD 052 | Serial Terminals and Serial System Interfaces |

| DEC STD 102 | Environmental Standards                       |

| DEC STD 103 | Electromagnetic Compatibility                 |

| DEC STD 104 | Acoustic Noise Acceptability                  |

| DEC STD 119 | Product Safety                                |

|             |                                               |

INTRODUCTION 1-3

| DEC STD 122 | AC Power Line Standard             |

|-------------|------------------------------------|

| DEC STD 134 | DEC Ethernet Specification         |

| DEC STD 200 | DEC Remote Diagnosis Specification |

The following documents are provided to guide customers in the installation and use of the system:

VS4000 VLC Hardware Installation Guide VS4000 VLC Owner's Manual VS4000 VLC Network Guide VS4000 VLC Maintenance Guide VS4000 VLC Technical Manual

# **1.4 Notation Conventions**

*Physical memory addresses* are expressed as eight hexadecimal digits punctuated with a period between the fourth and fifth digits for readability.

*Hexadecimal numbers* are denoted by a trailing "h", as for example FEh whose decimal equivalent is 254. All other numbers are decimal.

Interrupt vectors are given as three hexadecimal digits which are a byte offset into an SCB.

1-4 INTRODUCTION

# Chapter 2 CENTRAL PROCESSOR

The system central processor is a single CMOS chip fabricated in Digital's CMOS-3 process. This chip is fully described in its specification document which is cited in Section 1.3. This section covers the manner in which the chip is used by the VS4000 VLC; it does not attempt to reproduce all the material in the chip specification.

# 2.1 Processor Summary

The processor chip is a 32-bit virtual memory microprocessor with integral floating point capability and an on-chip cache, derived directly from the existing CVAX CPU, CFPA floating point unit and CVAX Clock chips. The chip is implemented in Digital's CMOS-3 process. Its key features are:

- 1. Subset of VAX data types: byte, word, longword, quadword, character string, and variablelength bit fields, support for f\_floating, d\_floating, and g\_floating point data types. Support for the remaining VAX data types can be provided by macrocode emulation.

- 2. Full base instruction group: integer and logical, address, variable-length bit field, control, procedure call, miscellaneous, queue, character string instructions CMPC3/CMPC5, LOCC, MOVC3/MOVC5, SCANC, SKPC and SPANC, and operating system support. F\_ floating, d\_floating and g\_floating point instructions are supported by the CFPA chip (including the floating point instructions that are part of the emulate-only instruction group: POLYf, EMULf, and ACBf). The remaining VAX instructions can be implemented via macrocode emulation. The chip provides microcode assists for emulation of the character string instructions which are not included in the full base instruction group, and the decimal string, EDITPC, and CRC instructions.

- 3. Full VAX memory management: includes a demand paged memory management unit which is fully compatible with VAX memory management. System space addresses are virtually mapped through single-level page tables; process space addresses are virtually mapped through double-level page tables. Supports four gigabytes (2\*\*32) of virtual memory and up to one gigabyte (2\*\*30) of physical memory.

CENTRAL PROCESSOR 2-1

- 4. On-chip memory cache: the processor chip has 8 KBytes of on-chip cache to improve execution times by minimizing the performance required of the memory subsystem. The cache is an eight set direct mapped write-through cache. To improve manufacturing yield, one or more of the eight sets may be disabled during the chip test process, allowing for possible die defects without causing the entire chip to be rendered unuseable. It is likely that a minimum of six sets will be functional. See Section 2.11.2.2

- 5. Single package: the CPU is packaged in a single 132-pin surface mounted cerquad package.

- 6. External data bus is 32 bits wide. External bus I/O cycles run at one half the internal bus speed. They may be lengthened in increments of one internal bus period to accommodate the timing requirements of various devices connected to the bus.

# 2.2 Differences from Full VAX Architecture

The principal differences between this processor chip and the full VAX architecture are these:

- 1. These data types are omitted: decimal string, octaword, and h\_floating. These data types can be supported by macrocode emulation.

- 2. These instruction classes are omitted: the three character string instructions MATCHC, MOVTC and MOVTUC, decimal string instructions, EDITPC, CRC, compatibility mode, octaword instructions, and h\_floating instructions. The chip provides microcode assists for the macrocode emulation of the character string, decimal string, CRC, and EDITPC instuctions.

- 3. These internal processor registers are omitted: NICR, ICR, TODR, RXCS, RXDB, TXCS, TXDB, and PME.

- 4. The chip does not have a built-in console function. (The console is implemented in the system firmware.)

# 2.3 Processor Clock

The oscillator that determines the CPU operating frequency connects directly to the CPU where it is divided by four to produce two anti-phase clocks for use outside the CPU. For a CPU internal cycle of 40 ns, the oscillator has a frequency of 106 MHz. and results in external clocks with a period of 160ns.

# 2.4 CPU DMA Access

The CPU DMA feature is used in performing cache invalidate cycles, using the fast-invalidate feature - see Chapter 4, Section 4.3.

# 2.5 Internal Processor Registers

The internal processor register (IPR) space provides access to many types of processor control and status registers such as the memory management base registers, parts of the process status longword, and the multiple stack pointers. These registers are explicitly accessible only by the privileged Move to Processor Register (MTPR) and Move from Processor Register (MFPR) instructions.

The following table enumerates the processor registers and indicates how they are implemented in the VS4000 VLC by one of the following codes:

| Ι | - | implemented as specified in the VAX Architecture Reference Manual (DEC STD 032). |

|---|---|----------------------------------------------------------------------------------|

| М | _ | implemented as specified in the Processor Chip Specification.                    |

| R | _ | access not allowed (reserved operand fault).                                     |

| X | _ | not implemented; read as zero, NOPed on write.                                   |

| Number | Name   | Description                | Note | Section |

|--------|--------|----------------------------|------|---------|

| 0      | KSP    | Kernel Stack Pointer       | Ι    |         |

| 1      | ESP    | Executive Stack Pointer    | Ι    |         |

| 2      | SSP    | Supervisor Stack Pointer   | Ι    |         |

| 3      | USP    | User Stack Pointer         | Ι    |         |

| 4      | ISP    | Interrupt Stack Pointer    | Ι    |         |

| 5      |        | not implemented            | Х    |         |

| 6      |        | not implemented            | Х    |         |

| 7      |        | not implemented            | Х    |         |

| 8      | P0BR   | P0 Base Register           | Ι    |         |

| 9      | P0LR   | P0 Length Register         | Ι    |         |

| 10     | P1BR   | P1 Base Register           | Ι    |         |

| 11     | P1LR   | P1 Length Register         | Ι    |         |

| 12     | SBR    | System Base Register       | Ι    |         |

| 13     | SLR    | System Length Register     | Ι    |         |

| 14     |        | not implemented            | Х    |         |

| 15     |        | not implemented            | Х    |         |

| 16     | PCBB   | Process Control Block Base | Ι    |         |

| 17     | SCBB   | System Control Block Base  | Ι    |         |

| 18     | IPL    | Interrupt Priority Level   | Ι    |         |

| 19     | ASTLVL | AST Level                  | Ι    |         |

| 20     | SIRR   | Software Interrupt Request | Ι    |         |

| 21     | SISR   | Software Interrupt Summary | Ι    |         |

| 22     |        | not implemented            | Х    |         |

| 23     |        | not implemented            | Х    |         |

Table 2–1: Processor Registers

CENTRAL PROCESSOR 2-3

| Number Name |        | Name Description                     |   | Section  |  |  |

|-------------|--------|--------------------------------------|---|----------|--|--|

| 24          | ICCS   | Interval Clock Control               | М | 2.5.3    |  |  |

| 25          | NICR   | Next Interval Count                  | Х |          |  |  |

| 26          | ICR    | Interval Count                       | Х |          |  |  |

| 27          | TODR   | Time of Year                         | Х |          |  |  |

| 28          |        | not implemented                      | Х |          |  |  |

| 29          |        | not implemented                      | Х |          |  |  |

| 30          |        | not implemented                      | Х |          |  |  |

| 31          |        | not implemented                      | Х |          |  |  |

| 32          |        | not implemented                      | Х |          |  |  |

| 33          |        | not implemented                      | Х |          |  |  |

| 34          |        | not implemented                      | Х |          |  |  |

| 35          |        | not implemented                      | Х |          |  |  |

| 36          |        | not implemented                      | Х |          |  |  |

| 37          | CCR    | Cache Control                        | Μ | 2-7      |  |  |

| 38          |        | not implemented                      | Х |          |  |  |

| 39          | MSER   | Memory System Error                  | М | 2.11.2.3 |  |  |

| 40          |        | not implemented                      | х |          |  |  |

| 41          |        | not implemented                      | Х |          |  |  |

| 42          | SAVPC  | Console Saved PC                     | Μ | 2.10     |  |  |

| 43          | SAVPSL | Console Saved PSL                    | Μ | 2.10     |  |  |

| 44          |        | not implemented                      | Х |          |  |  |

| 45          |        | not implemented                      | Х |          |  |  |

| 46          |        | not implemented                      | Х |          |  |  |

| 47          |        | not implemented                      | Х |          |  |  |

| 48          |        | not implemented                      | Х |          |  |  |

| 49          |        | not implemented                      | Х |          |  |  |

| 50          |        | not implemented                      | Х |          |  |  |

| 51          |        | not implemented                      | Х |          |  |  |

| 52          |        | not implemented                      | Х |          |  |  |

| 53          |        | not implemented                      | Х |          |  |  |

| 54          |        | not implemented                      | Х |          |  |  |

| 55          |        | not implemented                      | Х |          |  |  |

| 56          | MAPEN  | Memory Management Enable             | Ι |          |  |  |

| 57          | TBIA   | Translation Buffer Invalidate All    | Ι |          |  |  |

| 58          | TBIS   | Translation Buffer Invalidate Single | Ι |          |  |  |

| 59          |        | not implemented                      | Х |          |  |  |

| 60          |        | not implemented                      | Х |          |  |  |

| 61          |        | not implemented                      | Х |          |  |  |

| 62          | SID    | System Identification                | Ι |          |  |  |

| 63          | ТВСНК  | Translation Buffer Check             | Ι |          |  |  |

| 64:127      |        | reserved                             | R |          |  |  |

Table 2–1 (Cont.): Processor Registers

# 2–4 CENTRAL PROCESSOR

# 2.5.1 System Identification Register (SID)

The SID register (internal processor register 62, read-only) has the following format:

### Figure 2–1: System Identification Register (SID)

| 3<br>1         | 2<br>4 | 2<br>3      |          | 8           | 7         | 0   |

|----------------|--------|-------------|----------|-------------|-----------|-----|

| +<br>  TY<br>+ | PE     | +<br> <br>+ | reserved | +<br> <br>+ | microcode | rev |

The TYPE field has the value 20 (decimal) which identifies the processor as a DC222 processor chip. The contents of the "reserved" field are UNPREDICTABLE. The "microcode rev" field identifies the revision level of the chip internal microcode.

# 2.5.2 System Type Register (SYS\_TYPE)

The SYS\_TYPE register is a read-only longword contained in the system's main board ROM at physical address 2004.0004h. It has the following format:

### Figure 2–2: System Type Register (SYSTYPE)

| 3<br>1 | :        | 22  | 2        | 1 | 1 |            | 0 | 7                | 0 |

|--------|----------|-----|----------|---|---|------------|---|------------------|---|

|        | •        | + 3 | <b>)</b> | 0 | 5 |            | 0 | 1                | 0 |

|        | SYS_TYPE |     | revision |   |   | SYS_DEPEND |   | <br>  ARCH_IDENT | · |

The SYS\_TYPE field has a value of 4 which indicates that this is a VS4000 VLC. The revision field must be a non-zero value. The SYS\_DEPEND field is 0 or 1. The ARCH\_IDENT field is a value of 1.

# 2.5.3 Interval Clock Control and Status (ICCS)

The ICCS register (internal processor register 24, read/write) controls interval timer interrupts. It is similar to the ICCS register in the full VAX architecture but contains only a single bit to enable or disable the interval timer interrupt.

### Figure 2–3: Interval Clock Control and Status(ICCS)

| 3<br>1 |                                                                                                         |  |     |  |   |       |

|--------|---------------------------------------------------------------------------------------------------------|--|-----|--|---|-------|

| +      | 0                                                                                                       |  | IEN |  | 0 | •     |

|        |                                                                                                         |  |     |  |   | <br>F |

| <31:7> | Unused. Read as zero; ignored on write.                                                                 |  |     |  |   |       |

| IEN    | Interrupt Enable (bit 6). When this read/w<br>enabled. When it is clear, interval timer in<br>power-on. |  |     |  |   | -     |

| <5:0>  | Unused. Read as zero; ignored on write.                                                                 |  |     |  |   |       |

# 2.6 Reset and Power-On

The CPU chip input SYSRESET\_L is asserted (held LOW) during Power-on until the power supply voltage has risen to its operating level, it is then de-asserted asynchronously. The CPU synchronises this signal and produces a reset signal for use by the rest of the system - RESET\_L. This signal is de-asserted following a low to high transition of MCLKAO - one of the two clocks output by the CPU chip.

# 2.7 HALT

Logic external to the CPU asserts HALT\_L to transfer control to console microcode. At the completion of the current macro-instruction, the CPU enters the restart process with a restart code of 2. See Section 2.10

# 2.8 System Control Block

The System Control Block (SCB) consists of two physically-contiguous pages (1024 bytes) containing the vectors for servicing interrupts and exceptions. The start of the first of its pages is pointed to by the System Control Block Base (SCBB) internal processor register. The following table summarizes the vectors used by this system:

| Vectors | Name                         | Туре        | Notes |  |

|---------|------------------------------|-------------|-------|--|

| 000     | Passive Release              | Interrupt   | 4     |  |

| 004     | Machine Check                | abort       | 1     |  |

| 008     | Kernel Stack Invalid         | abort       |       |  |

| 00C     | Power Fail                   | interrupt   | 2     |  |

| 010     | <b>Resv/Priv Instruction</b> | fault       |       |  |

| 014     | Customer Resv Instr          | fault       |       |  |

| 018     | Reserved Operand             | fault/abort |       |  |

| 01C     | Reserved Addressing Mode     | fault       |       |  |

| 020     | Access Control Violation     | fault       |       |  |

| 024     | Translation Not Valid        | fault       |       |  |

| 028     | Trace Pending                | fault       |       |  |

2-6 CENTRAL PROCESSOR

| Vectors | Name                   | Туре       | Notes |  |

|---------|------------------------|------------|-------|--|

| 02C     | Breakpoint Instruction | fault      |       |  |

| 030     | unused                 |            |       |  |

| 034     | Arithmetic             | trap/fault |       |  |

| 038 03C | unused                 | -          |       |  |

| 040     | СНМК                   | trap       |       |  |

| 044     | CHME                   | trap       |       |  |

| 048     | CHMS                   | trap       |       |  |

| 04C     | CHMU                   | trap       |       |  |

| 050     | unused                 |            |       |  |

| 054 05C | unused                 |            |       |  |

| 060     | Memory Error           | interrupt  | 2     |  |

| 064 0C  | unused                 |            |       |  |

| 080     | Interprocessor         | Interrupt  |       |  |

| 084 0BC | Software levels 1-15   | interrupt  |       |  |

| 0C0     | Interval Timer         | interrupt  | 3     |  |

| 0C4     | unused                 |            |       |  |

| 0C8     | Emulation Start        | fault      |       |  |

| 0CC     | Emulation Continue     | fault      |       |  |

| 0D0 0FC | unused                 |            |       |  |

| 100 1FC | Adapter Vectors        | interrupt  |       |  |

| 200 3FC | Device Vectors         | interrupt  | 4     |  |

Notes:

- 1. See Section 2.9.1.

- 2. See Section 2.9.

- 3. See Section 2.9.2.

- 4. See Chapter 3.

# 2.9 Interrupts and Exceptions

Both interrupts and exceptions divert program execution from its normal flow by pushing the processor status and program counter onto the stack and then beginning execution at the address found in one of the interrupt vectors in the system control block (SCB). Interrupts and exceptions can arise either from conditions detected within the processor chip or from external signals sent to the processor chip. The internally detected cases are fully described in the processor chip specification; they are not further discussed here.

External interrupt causes are signalled to the processor via one of nine signals:

| Signal | Description            | Vector | IPL | Notes    |

|--------|------------------------|--------|-----|----------|

| ERR    | External machine check | 004    |     | not used |

| PWRFL  | Power fail             | 00C    | 1E  | not used |

| Signal | Description         | Vector | IPL | Notes                  |

|--------|---------------------|--------|-----|------------------------|

| MEMERR | Memory error        | 060    | 1D  | not used               |

| CRD    | Corrected Read Data | 054    | 1A  | not used               |

| IRQ3   | Device interrupt    |        | 17  | not used               |

| INTTIM | Interval timer      | 0C0    | 16  | see Sec-<br>tion 2.9.2 |

| IRQ2   | Device Interrupt    |        | 16  | not used               |

| IRQ1   | Device interrupt    |        | 15  | see Chapter 3          |

| IRQ0   | Device interrupt    |        | 14  | not used               |

The PWRFL, MEMERR, CRD, IRQ3 IRQ2 and IRQ0 signals are not used. Their pins are tied permanently to the inactive state so that the processor will never generate the corresponding interrupts.

The IRQ1 signal is generated by the interrupt controller which is described in chapter 3. This controller receives interrupt requests from all the I/O devices in a VS4000 VLC system and generates the appropriate vector for each source.

# 2.9.1 Machine Check Exceptions

A machine check exception results from either an internal processor of floating point unit error, or external response on the CPU ERR L line. In response to a machine check exception, the following parameters are pushed on the stack:

### Figure 2–4: Machine Check Exception Stack Data

| +<br>  byte count (0000.0010h) | +<br>  :SP                                       |

|--------------------------------|--------------------------------------------------|

| machine check code             | +                                                |

| most recent virtual address    | <pre>+ + + + + + + + + + + + + + + + + + +</pre> |

| internal state data 1          | See CPU spec.                                    |

| internal state data 2          | -<br>  II II II<br>-                             |

| PC                             | PC at start of instruction                       |

| PSL                            | Current PSL<br>+                                 |

2-8 CENTRAL PROCESSOR

| Machine<br>check<br>code (HEX) | Reason                                 |

|--------------------------------|----------------------------------------|

| 1                              | FPA protocol error                     |

| 2                              | FPA reserved instruction               |

| 3                              | FPA unknown error                      |

| 4                              | FPA unknown error                      |

| 5                              | process PTE in P0 space (TB miss)      |

| 6                              | process PTE in P1 space (TB miss)      |

| 7                              | process PTE in P0 space (M = 0)        |

| 8                              | process PTE in P1 space (M = 0)        |

| 9                              | undefined interrupt IPL code           |

| А                              | impossible microcode state (MOVCx)     |

| 80                             | read bus error, normal read            |

| 81                             | read bus error, SPTE, PCB, or SCB read |

| 82                             | write bus error, normal write          |

| 83                             | write bus error, SPTE or PCB write     |

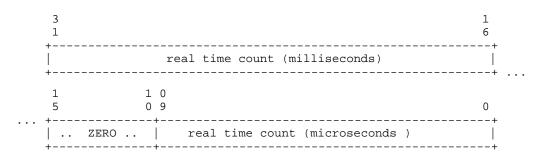

# 2.9.2 Interval Timer Interrupt

An interval timer interrupt request is generated every 10 milliseconds by a signal on the INTTIM pin which is derived from the serial line clock crystal. This interrupt is at IPL 16h and uses interrupt vector 0C0h. The ICCS processor register (see Section 2.5.3 contains a mask bit to enable or disable the interval timer interrupt.

# 2.9.3 Device Interrupts

Interrupt requests from the system's I/O controllers are collected by the interrupt controller (described in Chapter 3 of this specification) which ranks their priority and presents a single interrupt request to the processor on its IRQ1 pin. All such interrupt requests are presented at IPL 15h - see Figure 3–4. The number of the interrupt vector is determined by the interrupt controller according to the identity of the requesting I/O controller; the values are given in Section 3.7.

# 2.10 Processor Restarts

When the processor is signalled via the SYSRESET\_L or HALT\_L pins, or when it detects severe corruption of its operating environment, it performs a restart process which saves some context in internal processor registers SAVPC and SAVPSL, changes to unmapped mode, and begins execution in the system ROM at address 2004.0000h. Bits <13:8> of SAVPSL contain a *restart code* which indicates the cause of the restart. The VS4000 VLC console firmware determines which restarts are delivered to the operating system and which are displayed on the operator's console. The restart codes (in hex) are:

CENTRAL PROCESSOR 2-9

| Code | Reason                                                |

|------|-------------------------------------------------------|

| 2    | HALT asserted (see Section 2.10.2 below)              |

| 3    | Power on                                              |

| 4    | Interrupt stack not valid during exception            |

| 5    | Machine check normal exception                        |

| 6    | HALT instruction executed in kernel mode              |

| 7    | SCB vector bits $\langle 1:0 \rangle = 11$            |

| 8    | SCB vector bits $\langle 1:0 \rangle = 10$            |

| А    | CHMx executed while on interrupt stack                |

| 10   | ACV or TNV during machine check exception             |

| 11   | ACV or TNV during kernel stack not valid exception    |

| 12   | machine check during machine check exception          |

| 13   | machine check during kernel stack not valid exception |

| 19   | PSL<26:24> = 101 during interrupt or exception        |

| 1A   | PSL<26:24> = 110 during interrupt or exception        |

| 1B   | PSL<26:24> = 111 during interrupt or exception        |

| 1D   | PSL < 26:24 > = 101 during REI                        |

| 1E   | PSL < 26:24 > = 110 during REI                        |

| 1F   | PSL<26:24> = 111 during REI                           |

Table 2–2: CPU Restart Codes

The restart process sets the state of the chip as follows:

| SAVPC  | saved PC                                                                                                                    |

|--------|-----------------------------------------------------------------------------------------------------------------------------|

| SAVPSL | saved PSL<31:16, 7:0> in <31:16, 7:0><br>saved MAPEN<0> in <15><br>valid stack flag in <14><br>saved restart code in <13:8> |

| SP     | interrupt stack pointer                                                                                                     |

| PSL    | 041F0000 (hex)                                                                                                              |

| PC     | 2004 0000 (hex)                                                                                                             |

| MAPEN  | 0                                                                                                                           |

| SISR   | 0 (power-on only)                                                                                                           |

| ASTLVL | 4 (power-on only)                                                                                                           |

| ICCS   | 0 (power-on only)                                                                                                           |

| MSER   | 0 (power-on only)                                                                                                           |

| CADR   | 0 (power-on only)                                                                                                           |

|        | all else undefined                                                                                                          |

2–10 CENTRAL PROCESSOR

### 2.10.1 Power-on Restart

When system power is applied, the processor is signalled via the SYSRESET\_L pin. It performs a processor restart with a restart code of 3.

### 2.10.2 HALT Restarts

When the CPU is signalled via its HALT\_L pin, it performs a processor restart with a restart code of 2. Two things can generate such a signal:

- pressing the operator's CONSOLE MODE button

– receipt of a BREAK signal from serial line 3 when the Operator's ALTERNATE CONSOLE switch has been set to select this line as the console device.

Upon receipt of a HALT signal, the system enters console mode. Operation in this mode is controlled by the firmware in the main board ROM, which is described in the KA48 System Firmware Specification.

# 2.11 Cache General Description

This section describes the operation of the CPU's cache. The VS4000 VLC differs from the KA44 System in that it has ONLY a primary cache.

### 2.11.1 Organization and Addressing

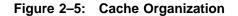

Each cache *set* consists of an array of *entries*. Each entry contains a *valid* flag, a *tag*, and a *data* block. There are a total of eight possible sets making up the CPU internal cache.

The data block holds 8 bytes (b=3) which are a copy of an aligned quadword in main memory. In each cache set, there is just one entry in which a copy of a given main memory quadword can be found. That entry is selected by an *e*-bit entry index which is extracted from the quadword's physical address. However, there are numerous quadwords which could occupy one cache entry, so they are distinguished by a *t*-bit tag which is also extracted from the quadword's physical address. The breakdown of the 30-bit VAX physical address is shown below:

CENTRAL PROCESSOR 2-11

Figure 2–6: General Cache Address Mapping

| 22  |        |        |     |     |

|-----|--------|--------|-----|-----|

| 98  |        |        | 32  | 0   |

| +-+ |        | +      | +   | +   |

| 0   | t bits | e bits | b b | its |

| +-+ |        | +      | +   | +   |

Starting from bit 0, the value of *b* depends on the size of the data block, which in this system is 8 bytes, so *b* is 3 - (2 <sup>3</sup> = 8). The values of *e* and *t* depend upon how many entries are in the set. For this CPU cache, there are 128 entries in each set, so e=7 and t=19.

Each entry's valid flag V indicates whether the entry contains a valid copy of data from main memory. The hardware automatically sets the valid flag whenever a processor read cycle stores data in the entry. All the valid flags in the caches must be cleared under program control before the caches are enabled after a period of processor operation with the caches disabled, since main memory data may have been changed during this period.

### 2.11.2 Control Registers

There are four registers associated with the memory system. The two associated with the cache control are the Cache Control Register which sets the mode of operation of the cache, is used in flushing the cache and provides an overall enable/disable function for the cache and the Bank-Enable Hit/Miss Register (BEHR) which enables/disables individual cache sets and provides information about the last cache cycle.

### 2.11.2.1 Cache Control (CCR)

#### Figure 2–7: Cache Control Register(CCR)- IPR 25h

| 3 |      | 0 0 0 0 0 |

|---|------|-----------|

| 1 |      | 4 3 2 1 0 |

| + |      | +-+-+-+   |

|   |      | CEFD      |

| 1 | /IBZ | WNLI      |

|   |      | P A U A   |

| + |      | +-+-+-+   |

- <31:04> Not used. Read as zeros; ignored on write.

- <03> Compare Wrong Parity. This bit is read/write and is for diagnostic use. When set, it inverts the sense of the data parity bits accessed from the cache. This will cause a parity error to be indicated and so may be used to check the parity generate/check logic associated with the cache. This bit does not affect Tag parity.

- <02> Enable Cache. This bit is read/write. When set, normal operation of the cache is enabled and both I and D-Stream references will be stored in those banks of the cache selected by Enable\_Bank<7:0> of the BEHR. This bit is cleared by SYSRESET\_L.

### 2–12 CENTRAL PROCESSOR

- <01> Flush\_Cache. This bit is write-only and reads always as zero. Writing a one to this bit clears all valid bits in all the cache tag arrays.

- <00> Diagnostic Mode. This bit is read-write. When it is set, the cache and BEHR register may be accessed via a region in I/O address space; when clear, references to that same region of I/O address space become normal external bus cycles.

Table 2–3:

Diagnostic Mode Cache Address Ranges

| BEHR       | 2015.0800 - 2015.0FFF |

|------------|-----------------------|

| Cache Data | 2015.0400 - 2015.07FF |

| Cache Tags | 2015.0000 - 2015.03FF |

When diagnostic mode is set, writes to the cache data addresses will write to the cache data longword indexed by address bits <09:02>. All banks that have the BEHR Enable\_Bank bit set will be written. Reads will return data from the highest priority bank if more than one bank is enabled.

Writes to cache tag addresses write to the cache tag indexed by bits <09:03> of the address. All banks that have their Enable\_Bank bit set in the BEHR will be written. The format of the data written is :-

Figure 2–8: Write Format, Tag Diagnostic Mode

| 3 3 2 2<br>1 0 9 8                |     | 1<br>0 | 0           | 0          |

|-----------------------------------|-----|--------|-------------|------------|

| +-+-+-+                           | TAG |        | ×X          | +<br> <br> |

| <br>  + VALID Bit<br>+ Tag Parity |     |        | r <b></b> - |            |

Reads from cache tag addresses read the cache tag addresses plus the data parity from the data longword addressed by bits<09:02> of the address as shown. If more than one Enable\_Bank bit is set, the data returned will be from the highest priority bank. (bank 0 is highest priority; 7 the lowest)

### Figure 2–9: Read format, Tag Diagnostic Mode

| 3 3 2 2<br>1 0 9 8 |                         |    | 1<br>0 | 0<br>9 | 0<br>4 | -  | 0<br>0 |

|--------------------|-------------------------|----|--------|--------|--------|----|--------|

| P V X <br>+-+-+-+  | T.                      | AG |        | Σ      | 2      | DP |        |

|                    | VALID Bit<br>Tag Parity |    |        |        |        |    | +      |

#### 2.11.2.2 Bank Enable/Hit Miss Register

The BEHR register is accessible as a longword ONLY, single bytes may not be written. It may be accessed at any of the longword addresses in the range 2015.0800:2015.0FFF when the CCR Diagnostic bit is set.

### Figure 2–10: Bank Enable/Hit Miss Register(BEHR)

| 3 |     | 1 | 1 | 0        | )  | 0 | 0 | 0  | 0   | 0   | 0     | 0     | 0   |

|---|-----|---|---|----------|----|---|---|----|-----|-----|-------|-------|-----|

| 1 |     | б | 5 | 8        | }  | 7 | 6 | 5  | 4   | 3   | 2     | 1     | 0   |

| + |     |   | + |          | -+ |   | + | +  | +   | +   | + - • | + - • | +-+ |

|   | MBZ |   |   | Bank     |    |   |   | Ε  | Bar | ık  |       |       |     |

| ĺ |     |   | İ | Hit/Miss | İ  |   |   | Er | nak | ole | e     |       | İ   |

| + |     |   | + |          | -+ |   | + | +  | +   | +   | + - • | +     | +-+ |

<31:16> MBZ. These bits are ignored on write and read always as zero.

- <15:08> BANK\_HIT<7:0> These bits are read-only and are provided for cache testing purposes. They reflect the Hit/Miss status of each of the banks of the cache for the most recent D-stream read or write cycle. A "1" indicates that there was a HIT in the corresponding bank of the cache, a "0" a MISS. These bits are cleared when SYSRESET\_L is asserted.

- <07:00> ENABLE\_BANK<7:0>. These bits are read/write and when set enable the respective banks of the cache. Note that the SOC cpu may have less than eight banks of cache functional and at chip test will have had those non-functional banks permanently disabled by lasar fusing. To determine how many and which banks of cache are functional on a particular chip, the ENABLE\_BANK bits should all be set by writing FFh to the BEHR register. The BEHR register should then be read and those bits of the ENABLE\_BANK field that return ones will indicate those banks of the cache that are actually enabled and useable. Whenever a bank is enabled or disabled, the cache should be flushed by writing a one to CCR<FLUSH>. ENABLE\_BANK<7:0> are cleared when SYSRESET\_L is asserted.

2-14 CENTRAL PROCESSOR

### 2.11.2.3 Memory System Error Register (MSER) - IPR 39h

This register is used to report information about the external CDAL bus and cache errors. Two types of errors are reported: those which do not cause an immediate problem in the operation of the CPU chip - these post an interrupt request; those which do cause an immediate problem and would disrupt the current instruction execution - these cause a machine check (trap via SCBB+4). The classification of errors into each type is discussed below.

| Figure 2–11: Memory System Error Register(MSE |

|-----------------------------------------------|

|-----------------------------------------------|

| 3<br>1                                |     | 7 | 6               | 5             | 4               | 3             | 0<br>2        | 1             | -                              |

|---------------------------------------|-----|---|-----------------|---------------|-----------------|---------------|---------------|---------------|--------------------------------|

| · · · · · · · · · · · · · · · · · · · | MBZ |   | B<br>  E<br>  R | C<br> P<br> E | D<br>  P<br>  E | T<br> P<br> E | T<br> P<br> 2 | T<br> P<br> 1 | I  <br>  N  <br>  T  <br>+ - + |

| <00> | Read-Write, INTERRUPT. This bit is set by the occurance of one of the interrupt       |

|------|---------------------------------------------------------------------------------------|

|      | type errors. Its setting causes an interrupt at IPL 1A and disables the cache. (Note  |

|      | that the ENABLE_CACHE bit in the CCR register will remain set). MSER<6:3>             |

|      | will indicate which error has occurred. Once this bit is set, MSER<6:3> will only be  |

|      | overwritten by TRAP type errors, subsequent INTERRUPT type errors will be lost.       |

|      | This bit is cleared by writing a one to this bit position on an IPR write to the MSER |

|      | and by RESET.                                                                         |

|      |                                                                                       |

- <01> Read-Write, TRAP1. This bit is set by the occurance of one of the trap type errors. Its setting causes a machine check abort and disables the cache. (Note that the ENABLE\_CACHE bit in the CCR register will remain set). MSER<6:3> will indicate which error has occurred. If bit<0>, INTERRUPT, was already set, this error will overwrite MSER<6:3>. This bit is cleared by writing a one to this bit position on an IPR write to the MSER and by RESET.

- <02> Read-Write, TRAP2. This bit is set by the occurance of one of the trap type errors, if TRAP1 has already been set and indicates a nested error. When this bit set, MSER<6:3> will indicate the error that had occurred when TRAP1 was set. The result of this bit being set is a machine check. This bit is cleared by writing a one to this bit position on an IPR write to the MSER and by RESET.

- <03> Read-only, Tag Parity Error. This bit is set when incorrect atg parity is detected in an enabled bank of the cache during a cache read or write operation. For D-stream reads that encounter this error, the result is a machine check, for all other cache cycles where the error occurs, the rsult is an interrupt.

- <04> Read-only, DAL Data Parity Error. This bit is set when incorrect DAL parity is detected on an external read cycle. For the first cycle of a D-stream read, it results in a machine check; for the second cycle of a D-stream read or an I-stream read, it results in an interrupt.

| <05>    | Read-only, Cache Data Parity Error. This bit is set when a cache data parity error is detected. On a D-stream error, the result is a machine check, for an I-stream error the result is an interrupt. |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <06>    | Read-only, Bus Error. This bit will be never be set for the VS4000 VLC system as the Error/Retry feature of the CPU is not used.                                                                      |

| <31:07> | Read-only, always return zero.                                                                                                                                                                        |

# 2.11.3 Diagnostic Operation

Refer to SOC chip spec 3.8.5

## 2.11.4 Cache Initialization

Before enabling the first-level cache after power-on or after operation with the cache disabled, all the valid flags in the cache must be cleared to ensure that no stale data will be read from the cache. This may be done by setting cache diagnostic mode (CCR<00> = 1), setting all the bank enable bits in the BEHR register and then writing all the tags in parallel with V=0.

# Chapter 3 INTERRUPT CONTROLLER

The interrupt controller is a part of the DC7201 and performs two separate functions.

- It receives up to eight interrupt request signals from the system's I/O devices, synchronises and latches them. The latched requests are then masked by individual Enable bits and the results ORed to form a single interrupt, presented to CPU on IRQ1 L, Interrupt Priority Level 15h.

- It recognises CPU Interrupt Acknowledge Cycles for IPL 14h, 15h, 16h and 17h and generates a ROM cycle to retrieve an appropriate vector.

# 3.1 IPL15h Interrupt

The eight interrupt request sources that result in an interrupt at IPL15h have associated with them three registers :-

- INT\_REQ holds the latched interrupt requests received from I/O devices (read-only).

- INT\_MSK contains a mask which determines which interrupt requests will generate a processor interrupt (read/write).

- INT\_CLR enables a program to selectively reset interrupt request bits in the INT\_REQ register (write-only).

The bits in each of these registers are uniformly associated with interrupt sources according to the numbering given in Section 3.3. For example, bit 0 in each register is associated with the SCSI controller interrupt.

The eight latches which comprise the INT\_REQ register are edge-triggered: each latch records an interrupt request from an I/O device when the device's interrupt request signal changes from false to true. The contents of the INT\_REQ register are ANDed with those of the INT\_MSK register, the results ORed to form an interrupt request to the CPU. The resulting interrupt request is presented to the CPU as IRQ1 L.

When the CPU acknowledges an interrupt request, the interrupt controller sends to it the interrupt vector associated with the highest-numbered bit which is set in both the INT\_REQ and INT\_MSK registers and clears that bit in the INT\_REQ register (the INT\_MSK bit is not affected). The interrupt vector values are listed in Section 3.7.

INTERRUPT CONTROLLER 3-1

Any set bit in the INT\_REQ register can also be cleared by a writing a byte to the INT\_CLR register which has a one in the corresponding bit position. (This is a transient operation; the data written is not stored and does not prevent the INT\_REQ bit from being set in the future). This enables a program to handle a device in non-interrupt mode by clearing the device's INT\_MSK bit, polling its requests by reading the INT\_REQ register, and clearing its requests by writing to the INT\_CLR register.

Since the bits of the INT\_REQ register are edge sensitive rather than level sensitive, a program which responds to a request from a device (either in an interrupt service routine or by polling the INT\_REQ register) and clears its bit in INT\_REQ must do whatever is necessary to return that device's interrupt request signal to its false state in order that a subsequent request from the device will be able to set its bit in INT\_REQ again.

Upon power-on, all bits in the INT\_REQ and INT\_MSK registers are cleared.

# 3.2 INTACK Cycles

For IPL 15h, the DC7201 generates a three bit number from the eight possible interrupt requests, using a fixed priority encoding, shifts this number 2 places to the left to form a number in the range <00:1C>h, then ORs this with the value 2004.0020h and presents the result - a number now in the range <2004.0020:2004.003C>h to the system ROM as a longword aligned address. The data which is retrieved from ROM is returned to the CPU to be added to the SCCB to form the interrupt vector specific to the highest priority interrupt currently active.

For IPL14h, 16h and 17h, a fixed address is presented to the system ROM from which a single interrupt vector for each level is retrieved.

| IPL | ROM Address (HEX)   |

|-----|---------------------|

| 14  | 2004.0040           |

| 15  | 2004.0020:2004.003C |

| 16  | 2004.0048           |

| 17  | 2004.004C           |

# 3.3 Interrupt Sources and Ranking

The eight interrupt sources that result in an IPL15h interrupt are listed in the following table. The interrupt numbers 7:0 indicate their bit positions in the INT\_xxx registers and their relative priority when more than one request is pending; 7 is the highest priority.

Interrupts 0, 1, 3. 4, 5 and 6 are dedicated to devices on the system board. Interrupts 2 and 7 come from optional devices.

| Num | Name | Source                                 |

|-----|------|----------------------------------------|

| 7   | SR   | unused                                 |

| 6   | ST   | 79C30 controller request for service   |

| 5   | AR   | Async. line receiver done or silo full |

| 4   | AT   | Async. line transmit done              |

| 3   | G1   | Graphics                               |

| 2   | G0   | Graphics                               |

| 1   | NI   | Network Controller                     |

| 0   | SC   | Storage controller                     |

Table 3–1: Interrupt Signal Sources

# 3.4 Interrupt Request Register (INT\_REQ)

The interrupt request register is an 8-bit read-only register at physical address 2008.000Fh each of whose bits reflects the state of the interrupt request latch for one interrupt source. Bits<7:0> correspond to interrupt numbers <7:0> as listed in Section 3.3.

### Figure 3–1: Interrupt Request Register (INTREQ)

| INT 7 | 6  | -  | =  | -  | —    | _  | -  | - |

|-------|----|----|----|----|------|----|----|---|

| NA    | SO | AR | AT | G1 | - G0 | NI | SC | İ |

A bit in the INT\_REQ register is set only by an active transition on the corresponding device's interrupt request line. The bit will be set by an active transition regardless of the state of the corresponding bit in the interrupt mask register, INT\_MSK. However, an interrupt request is sent to the CPU only when the corresponding bits in both INT\_REQ and INT\_MSK are set.

A bit in the INT\_REQ register is cleared either by a program which writes to the INT\_CLR register with a one in the corresponding bit position, or by a CPU interrupt acknowledge cycle during which the bit is the highest-numbered bit in INT\_REQ which is set and whose corresponding bit in the interrupt mask register INT\_MSK is also set.

INT\_REQ may be read at any time; reading it does not alter the state of the system in any way.

Upon power-on, the interrupt request register is cleared to zero.

INTERRUPT CONTROLLER 3-3

# 3.5 Interrupt Clear Register (INT\_CLR)

The interrupt clear register is an 8-bit write-only register at physical address 2008.000Fh which is used to selectively clear bits in the interrupt request register INT\_REQ. Bits 7:0 correspond to interrupt numbers 7:0 as listed in Section 3.3.

### Figure 3–2: Interrupt Clear Register (INT\_CLR)

| INT 7 | 6  | -  | =  | -  | _  | _  | -  |   |

|-------|----|----|----|----|----|----|----|---|

| +     | S0 | AR | AT | G1 | G0 | NI | SC | İ |

For each bit of INT\_CLR which is a one, the corresponding bit of INT\_REQ is cleared. For each bit of INT\_CLR which is a zero, the corresponding bit of INT\_REQ is not changed. The effect of writing to INT\_CLR is transient; its contents are not stored and writing to it does not prevent any INTREQ bits from being set in the future.

### WARNING

As INT\_REQ and INT\_CLR share the same address, use of a Read/Modify/Write instruction when accessing the INT\_CLR register could cause loss of interrupts.

# 3.6 Interrupt Mask Register (INT\_MSK)

The interrupt mask register is an 8-bit read/write register at physical address 2008.000Ch each of whose bits is a mask for one interrupt source. Bits 7:0 correspond to interrupt numbers 7:0 as listed in Section 3.3. Each mask bit is ANDed with the corresponding bit of the INT\_REQ register before being input to a priority encoder, the output of which determines which bit in INT\_REQ will be cleared (if more than one bit is set) when the CPU executes an Interrupt Acknowledge Cycle.

### Figure 3–3: Interrupt Mask Register (INT\_MSK)

| MSK 7 | - | -  | -  | -  | =  | —  | 0  |  |

|-------|---|----|----|----|----|----|----|--|

| NA    | • | AR | AT | G1 | G0 | NI | SC |  |

Note that a zero in a mask register bit does not prevent the corresponding device from setting its interrupt request register bit. If a request bit is set whose corresponding mask bit is zero, a CPU interrupt is not requested until the mask bit is subsequently set to one (assuming that the request bit has not meanwhile been cleared by writing to INT\_CLR). A program which is changing from polled to interrupt servicing of a device should be sure to clear the device's bit in INT\_REQ prior to setting its bit in INT\_MSK in order to avoid a possible false interrupt signal to the CPU.

Upon power-on, the interrupt mask register is cleared to zero.

# 3.7 Interrupt Vector Generation

When the CPU acknowledges an interrupt from the interrupt controller, the interrupt controller causes a vector number to be placed on the CDAL bus which corresponds to the highest priority pending interrupt. It obtains this vector number from reserved locations in the System Board ROM, Chapter 5, Section 5.1.

The vector presented to the CPU in an INTACK cycle has the following format

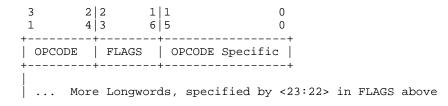

### Figure 3–4: Interrupt Vector Longword

| 3      | 1 0<br>0 9 | 0 0 0<br>2 1 0 |

|--------|------------|----------------|

| 0<br>+ |            | /NUM  0 P      |

| <31:10> | Zero.                                                                                                                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <09>    | Must be one.                                                                                                                                                                                                                                         |

| <08:02> | VNUM. Interrupt vector number which is multiplied by 4 to form an offset to a vector position in the current SCB. Since only vectors in the range 200h through 3FCh should be used for I/O devices, bits 15:10 are zero and bit 9 is a one.          |

| <01>    | Must be zero.                                                                                                                                                                                                                                        |

| <00>    | P. Priority level flag which selects the IPL to which the processor is<br>raised when it acknowledges the interrupt. If this bit is zero, the IPL<br>will be the interrupting IPL; if it is one, the IPL will be 17h. The normal<br>setting is zero. |

The conventional vector values established by the system ROM firmware for the various IPLs are as follows (the value in the Vect column represents bits 15:0 of the longword; the value in the P column is then placed in bit 0 of the longword):

INTERRUPT CONTROLLER 3-5

| <br>IPL | No | Name | Vect | Р | Source                                                         |

|---------|----|------|------|---|----------------------------------------------------------------|

| 15      | 7  |      |      |   | Unused                                                         |

| 15      | 6  | ST   | 02C4 | 0 | 79C30 request for service                                      |

| 15      | 5  | AR   | 0250 | 0 | Asynchronous serial line controller receiver done or silo full |

| 15      | 4  | AT   | 0254 | 0 | Asynchronous serial line controller transmit done              |

| 15      | 3  | G1   | 0244 | 0 | Graphics interrupt 1                                           |

| 15      | 2  | G0   | 0248 | 0 | Graphics interrupt 0                                           |

| 15      | 1  | NI   | 03F8 | 0 | Network controller                                             |

| 15      | 0  | SC   | 03FC | 0 | Storage controller                                             |

| 14      |    |      | 3F4  | 0 | Unassigned                                                     |

| 16      |    |      | 3F0  | 0 | Unassigned                                                     |

| 17      |    |      | 3EC  | 0 | Unassigned                                                     |

Table 3–2: Interrupt Vectors

### Note

The vectors listed above are subject to change; the System ROM Specification should be consulted for current values.

# 3.7.1 Passive Release

A special case occurs when the CPU executes an Interrupt Acknowledge Cycle and no interrupt is pending (INT\_REQ<7:0> = 00000000). This case can only occur when for some reason a write has occurred to INT\_CLR, with the interrupt system enabled, between the time that the interrupt controller has asserted IRQ1 L and the CPU initiates the Interrupt Acknowledge cycle. For this case, the interrupt controller does not access the System Board ROM, but internally generates a vector of all zeros.

# Chapter 4

# MAIN MEMORY

The memory controller allows for up to six memory SIMMs to be installed, in pairs, on the system module. The system module itself carries no memory. The SIMMs may be 256K x 36 or 1M x 36. All SIMM sockets must be populated with the same size SIMM. This gives possible memory capacities of 2, 4, 6, 8, 16 or 24 MBytes.

The six SIMM sockets have fixed addresses, depending upon the size of the SIMMs installed. For a small SIMM configuration, the first pair of SIMMs respond to addresses <0:1FFFFF>, the second pair to <200000:3FFFFF>, the third pair to <400000:5FFFFF>. For a large SIMM configuration, the first pair respond to addresses <0:7FFFFF>), the second pair to addresses <800000:FFFFFF> and the third pair to <1000000:17FFFFF>.

The DC7201 arbitrates between and services requests for main memory cycles from several sources; the CPU, the Ethernet Controller (NI), the Storage Controller (SCSI) and the Graphics Controller (GC) section of the memory controller. To optimize use of the available RAM bandwidth, data to/from these several requestors is buffered within the DC7201. To further minimize interaction between the requestors, the DC7201 has three data busses; the CDAL which connects it to the CPU; the EDAL which connects it to the NI, SCSI and Invalidate Filter and the MDAL which connects to the memory system, including the Video RAMS which make up the integral frame buffer.

The memory controller is capable of performing several types of RAM cycles; longword, quadword and octaword. Buffering between the several requestors and the memory allows these various cycles to be used in a way that makes best use of the available memory bandwidth. The sections that follow will discuss each requestor and the cycles generated.

The NI and SCSI controllers are DMA devices; the GC can generate addresses independently. Thus all three of these devices may attempt to write to memory locations that are currently cached. To maintain cache coherency it is necessary that for all writes requested by any of these devices, the CPU cache be checked and, if necessary, an entry invalidated. This could impose a significant load on the CPU to check the potential invalidates. For this reason the DC7201 controls a separate invalidate filter (backmap) which maintains a copy of the CPU's cache tags. In this way only those writes that do require a cache invalidate will disturb the CPU.

MAIN MEMORY 4-1

To allow greater flexibility, the two DMA devices access memory via a translation map contained in memory - see Section 4.4. The GC address generator performs virtual access to memory via the page tables - refer to the PVAX2 Graphics Controller Specification for further information.

# 4.1 Main Memory Requests

Main memory requests have a fixed priority, as follows (highest to lowest) :

- GC shift register load

- GC cursor buffer load

- Refresh

- NI Controller

- CPU

- SCSI Controller

- GC Address Generator

Refer to the PVAX2 Graphics Controller Specification for details of all GC functions.

# 4.1.1 NI Controller

The NI Controller is one of the requestors connected to the EDAL bus. It contends with the SCSI controller and the Invalidate Filter for access. The DC7201 maintains input and output buffers for the 16-bit wide data received from and to be sent to the NI Controller.

For NI controller data transfers to the DC7201, the 16-bit data words are accumulated within the DC7201 until a quadword address boundary is crossed or until the address of the next received data is seen to be no longer in sequence. This accumulated data is then written to memory in a single operation. For transfers that start at a quadword aligned address, the write to memory will be a page-mode quadword cycle. For transfers that start at a longword aligned address, the first write to memory will be a longword write of four bytes. For transfers that start at a non-longword aligned word address, the first write to bytes <3:2> only. In either of these two non-quadword aligned cases, after this initial alignment write has occurred, all subsequent sequential transfers will cause page-mode quadword cycles. An interrupt from the NI Controller or a timeout - no data transfer from the NI Controller to the DC7201 within <<<tbody>

Requests from the NI Controller for data from memory that present a quadword aligned address will cause the DC7201 to retrieve a quadword of data from memory. The three additional 16-bit words read in addition to the word actually requested by the NI Controller remain buffered within the DC7201 to satisfy the (assumed) next three read requests from the NI controller. For non-quadword aligned address requests the DC7201 retrieves the longword of data that includes that actual word requested. Depending on the actual address alignment, the second word of this data may be used to fill the next NI Controller request or may be discarded.

### 4-2 MAIN MEMORY

This buffer/lookahead read mechanism is totally transparent to software, the operating system driver need have no knowledge that this is happening, but should be aware that progem loops that rely on exact timings may show inconsistencies.

All memory write requests that originate from the NI Controller are passed to the invalidate filter logic as the write occurs to memory - see Section 4.3.

# 4.1.2 SCSI Controller

The SCSI Controller is one of the requestors connected to the EDAL bus. It contends with the NI controller and the Invalidate Filter for access. The DC7201 maintains input and output buffers for the 16-bit wide data received from and to be sent to the SCSI Controller.

For SCSI controller data transfers to the DC7201, the 16-bit data words are accumulated until a quadword address boundary is crossed or until the address of the next received data is seen to be no longer in sequence. This accumulated data is then written to memory in a single operation. For transfers that start at a quadword aligned address, the write to memory will be a page-mode quadword cycle. For transfers that start at a longword aligned address, the first write to memory will be a longword write of all four bytes. For transfers that start at a non-longword aligned word address, the first write to memory will be a longword write to bytes <3:2> only. For transfers that start at a non-word aligned byte address the first write to bytes <3:2> only. For transfers that start at a non-word aligned byte address the first write to memory will be a longword write to byte<3> only. For all of these non-quadword aligned cases, after this initial alignment write has occurred, all subsequent sequential transfers will cause page-mode quadword cycles. An interrupt from the SCSI Controller or a timeout - no data transfer from the SCSI Controller to the DC7201 within <<<tbody>

Requests from the SCSI Controller for data from memory that have a quadword aligned address will cause the DC7201 to retrieve a quadword of data from memory. The three additional words read in addition to the word actually requested by the SCSI Controller remain buffered within the DC7201 to satisfy the (assumed) next three read requests from the SCSI controller. For non-quadword aligned address requests the DC7201 retrieves the longword of data that includes that actual word requested. Depending on the actual address alignment, the remainder of this data may be used to fill the next SCSI Controller request(s) or may be discarded.

This buffer/lookahead read mechanism is totally transparent to software, the operating system driver need have no knowledge that this is happening.

All memory write requests that originate from the SCSI Controller are passed to the invalidate filter logic as the write occurs to memory - see Section 4.3.

### 4.1.3 CPU Memory Requests

The CPU can request longword or quadword read cycles and up to longword (specified by a four-bit byte mask) write cycles. As the CPU's internal cache is write-through, all CPU generated writes appear immediately as write requests to the DC7201. The DC7201 contains a two quadword write buffer for CPU write requests so that longword write requests to sequential longword addresses may be passed to the memory controller as quadword write requests to take advantage of the faster page-mode cycles possible when writes are performed to sequential addresses within the same page.

MAIN MEMORY 4-3

# 4.2 Write Buffer and Read Requests

Data may be retained within the DC7201 write buffer for some considerable time if writes are infrequent. For this reason the DC7201 allows read requests to be executed without flushing the write buffer. On any CPU generated read request when the write buffer is not empty, the DC7201 first compares the requested address with the address(es) of the data in the write buffer; if a match occurs, the data is returned to the CPU from the write buffer altough, for control simplicity, a memory read is still executed; the read data being ignored. If only a part of the requested data is found in the write buffer, the memory read supplies the missing bytes, the write buffer contents are not altered. If the requested data is not found in the write buffer, memory data is supplied to the CPU.

# 4.2.1 Write Buffer Flushing

Certain operations require that the data in the DC7201 write buffer be written back to memory before these operations are allowed to occur. The DC7201 makes this determination and ignores any CPU-generated *Clear Write Buffer* cycles.

The DC7201 will write back all data contained in its write buffer when it receives a request for a read or write to any address in I/O space (address bit  $\langle 29 \rangle = 1$ ) or when it recognises an INTACK Cycle. In both these cases, the data in the write buffer is first written to memory, then the I/O read or write occurs or the ROM read (INTACK) occurs. The result at the end of either operation is that the write buffer is empty.

# 4.3 Invalidate Filter

The DC7201 controls two 2K x 8 SRAMs where a copy of the CPU tag store is maintained. On CPU cache allocates, the tag value is written into this RAM. As the CPU cache is multiple set, it is necessary to maintain up to eight separate tag values for any given Index in this RAM. On any write generated by the NI, SCSI or GC, the eight entries are checked for a possible invalidate request to be passed back to the CPU. Only if a match is found will be CPU be disturbed and the entry in the invalidate filter SRAM be cleared. CPU invalidates are requested by assertion of the CPU DMA Request line and then executing a quadword or octaword fast invalidate cycle.

# 4.3.1 Invalidate Filter Cache Set Selection - CAC\_LIM

The CPU may have from one to eight cache sets active. To minimize the overhead of the Invalidate Filter lookup operation when less than a full eight sets are active, a limit register is provided which may be loaded with the maximum set number. This register, CAC\_LIM, is accessible at address 2008.0018h. Only bits <2:0> have significance and specify the maximum cache set number directly. The value to be loaded into this register is established by initially loading the CPU Bank Enable register, see Chapter 2, Section 2.11.2.2, then reading that same register. The bit pattern returned in bits<7:0> indicates which cache sets are active and enabled. This bit field should then be converted into a three bit number and loaded into CAC\_LIM.

CAC\_LIM is initialized on power-on to <111> to select all eight cache sets.

### 4-4 MAIN MEMORY

### 4.3.2 Invalidate Filter Initialization

Prior to enabling the CPU cache, the Invalidate Filter must be initialized so that it represents a copy of the initial CPU cache state, i.e. no entries cached. This is done by accessing the Invalidate Filter RAMs via a range of I/O addresses, 2020.0000:2020.0FFCh. Writes to sequential longword addresses in this range with data of zero will initialize the filter RAMs.

Following intialization, the Filter should be enabled by writing to bit <FILT\_ENA> in the BWF0 Register - see Chapter 6, Section 6.6.

# 4.4 DMA Mapping

The NI and SCSI controllers access memory via a translation table which is contained in main memory. A Map Base Address Register - MAP\_BASE - within the DC7201 points to the beginning of this reserved region of memory. The 32,768 longwords extending upwards from MAP\_BASE provide translations for the page address supplied by either DMA device. Each DMA device has a two-entry cache of current translations (one for read, one for write) kept within the DC7201. It is the responsibility of the operating system to allocate entries for each DMA device in this common translation table.

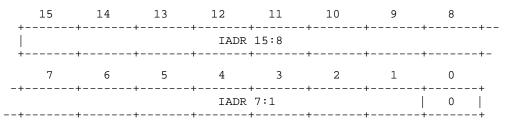

### Figure 4–1: Map Base Register MAP\_BASE - Address 2008.0008

| 3<br>1 |         | 2 2 5 4     |      | 1<br>7      | 1<br>6 | 0 |

|--------|---------|-------------|------|-------------|--------|---|

| +      | IGN<br> | <br> <br>-+ | BASE | <br> <br> + | IGN    | + |

- <1:25> IGN. Ignored on write, read as zero.

- <24:17> BASE<7:0>. Specifies the start of a 32 K longword region in main memory. The longwords specified by this address and the 32,767 longwords that follow contain translation entries for DMA devices.

<15:00> IGN. Ignored on write, read as zero.

## 4.4.1 Translation Table Entry Format

Although the space allocated for the DMA translation table is 32,768 longwords, the actual space used is a function of the starting addresses supplied to each of the DMA devices and the maximum transfer length allowed.

Any of the 32,768 longwords allocated for DMA translation entries must be written in the following format prior to initiating any DMA transfer :

MAIN MEMORY 4-5

### Figure 4–2: Translation Entry Format

| 3 3               |     | 1 1         | 0           |

|-------------------|-----|-------------|-------------|

| 1 0               |     | 8 7         | 0           |

| +-+<br> V <br>+-+ | IGN | PAGE NUMBER | +<br> <br>+ |

- <31> Valid Bit. Indicates to the DMA translation hardware within the DC7201 that this location contains a valid page number for use in translation. The operating system must set this bit for all translation table entries that it expects to be used.

- <30:18> IGN these bits are ignored.

- <17:00> Page Number, the longword aligned start address of a 512 byte region of memory allocated as a part of a buffer for one of the DMA devices. The eighteen bits specified in this field allow for a maximum memory size of 128 MBytes.

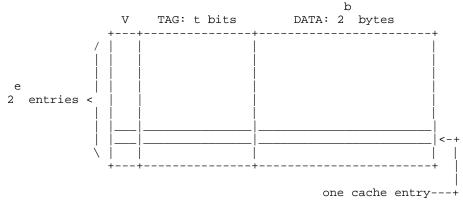

### 4.4.2 Translation

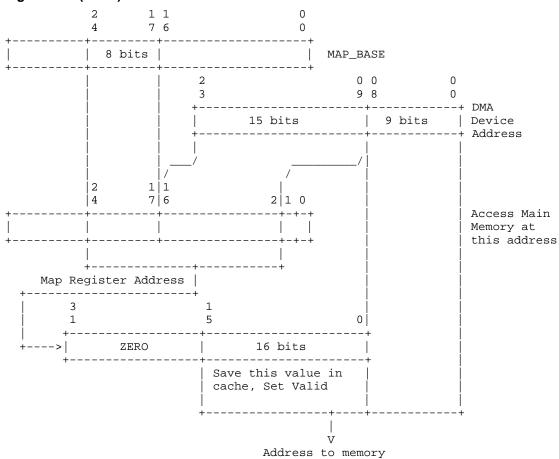

Each DMA controller has its own 24-bit address counter for DMA transfers that has a page field - 15-bits and an address-within-page field - 9-bits. When a DMA controller presents an address to the DC7201 to perform a DMA cycle to/from main memory, the DC7201 translates the address supplied, using MAP\_BASE and the translation table contained in main memory as follows. Bits <23:09> of the address supplied by the DMA controller - the page field - are compared to the address value held in either the read or write translation cache (as appropriate) for that DMA device. If the addresses match and if that entry is marked as Valid, the associated page address held in a field of that cache entry is concatenated with the address-within-page field of the supplied address to form the actual address to be used and the DMA cycle proceeds.

If the address match fails, indicating that this DMA transfer is to an address on a different page from the last DMA transfer that this device initiated, bits <23:09> of the DMA address supplied are concatenated with bits <24:17> of MAP\_BASE to form a new 23-bit longword aligned map register address. This address is then used to retrieve data from the translation table in main memory. Bits <15:00> of the data returned from memory are then concatenated with the original address-within-page bits supplied by the controller to form a 25-bit address that is the actual address to be accessed. Bits<15:00> that were retrieved from the translation table are stored as a new value in the appropriate translation cache associated with that DMA device and the Valid bit set for that entry.

4-6 MAIN MEMORY

Byte 2 <-- Unmapped page --> 0 0 within 0 3 Address 9 8 Page 0 \_\_\_\_\_ ----+ DMA | 15 bits | 9 bits | Device \_\_\_\_\_ ---+----+ Address / / / 3 3 1|1 <--- Mapped Page --> 0 1 0 6 5 Address 0 +-+-----+ Cached |V| 16 bits Entry <-\_ \_ in DC7201 -+-----+-+-----+ \_\_\_\_\_ --+-----+----+ + V Address to memory

Figure 4–3: DMA Address Translation - Translation Cache Hit

Figure 4–4: DMA Address Translation - Translation Cache Miss

Figure 4-4 Cont'd on next page

MAIN MEMORY 4-7

### Figure 4–4 (Cont.): DMA Address Translation - Translation Cache Miss

### 4.4.3 Example

As noted above, the actual memory space that need be allocated for translation entries can be up to 32,768 longwords. In many cases, less than this may be used. Consider, for example, that the two DMA devices of the system are restricted to maximum transfers of 64 KBytes, with only a single buffer available for each device. This requires that only 104 pages be allocated for each device.

The defined bit positions in MAP\_BASE imply that the translation buffer must be aligned on a 104 KByte address boundary, and indeed, if the full 24-bit addressing capability of the DMA devices is to used, this is necessary. However, in the example being considered, we need only to define 104 contiguous entries for each device, the translation table can be offset from a 104 KByte address boundary by suitably modifying the start address supplied to each DMA controller; remember that it is the concatenation of the page address of the DMA controller address and MAP\_BASE that forms the address from which the actual page address will be retrieved.

### 4-8 MAIN MEMORY

e.g. MAP\_BASE = 40000h; SCSI Controller Start address = 1000h